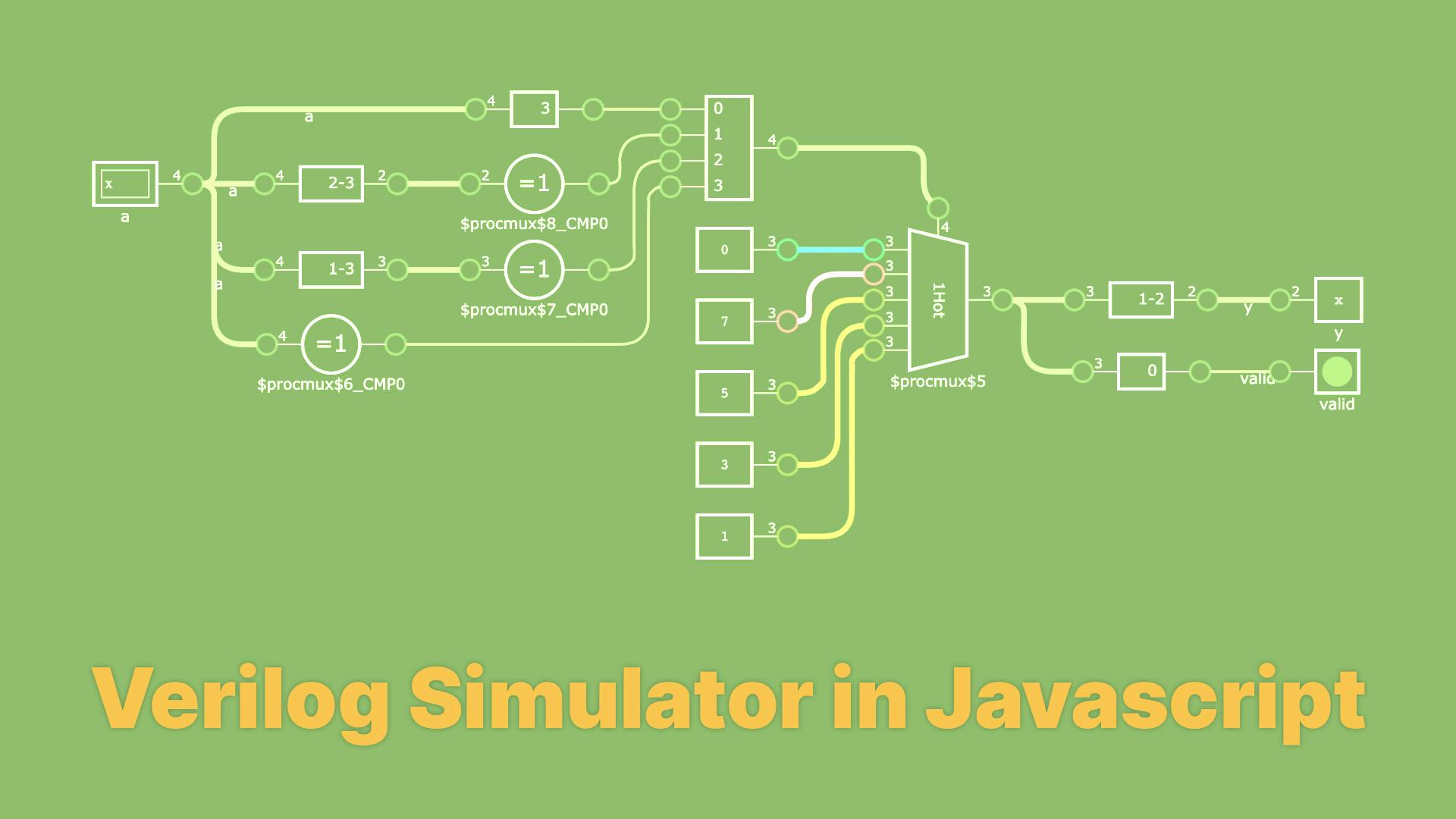

Imagesource: http://digitaljs.tilk.eu/

Verilog, System Verilog and VHDL all have something in common. In interaction with a FPGA they are all wonderfully suitable to make exciting hardware experiments. From your own 8-bit or RISC CPU over various logic circuits to your own VGA output module - the only limit is your imagination.

And affordable FPGAs are available these days - nothing stands in the way of experimentation.

Unless you are not familiar with at least one of the first three up there. Some are held back by the logical step from circuit design to formal implementation. Others struggle with creating test benches or the complexity of existing tool chains.

In Issue #48 we already spoke about a nice alternative, today we follow up again.

Marek Materzok is the developer of DigitalJS and provides a version that runs in the browser on his website.

Marek limits himself to the Verilog derivatives, there is no VHDL integration yet. But besides Verilog and System Verilog, hex files as well as Lua scripts can be loaded, synthesized, and then provided with a clock signal. A special feature is, that the components cast into code are automatically visualized with the help of ElkJS or Dagre. LogiSim backwards, so to speak.

Really beautiful project that invites to experiment and learn. Especially because a number of modules are included in the form of loadable sample code, and you can also upload and synthesize you own files.

Read the full newsletter Issue #54 of 8bitnews.io: Verilog in the Browser

More from #54

Don't want to miss updates like that? Subscribe below and receive regular content that we only share with our subscribers.